[i] Расчет времени преобразования АЦП и время заряда внутренней емкости

Расчёт и измерение времени преобразования АЦП

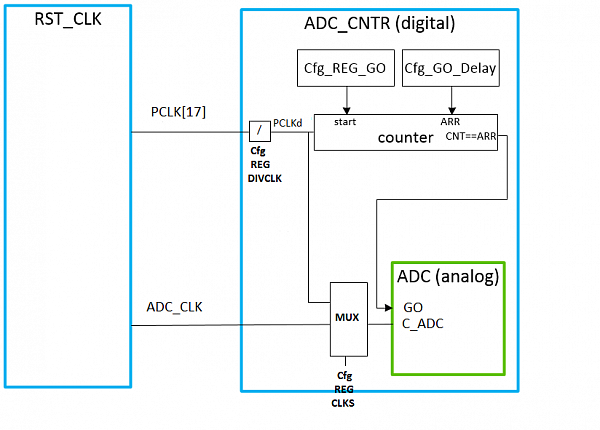

Структурная схема блока АЦП представлена на рисунке 1.Рисунок 1 - Структурная схема блока АЦП

Рассчитаем время преобразования АЦП. Для микроконтроллеров К1986ВЕ1QI, К1901ВЦ1QI , К1986ВЕ92QI , К1986ВК214 и К1986ВК234 общее время преобразования АЦП определяется по формуле 1:

где T_C_ADC - период частоты, на которой работает блок АЦП, [c];

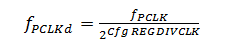

T_PCLKd - период частоты f_PCLKd (формула 2), [c];

DealyGo - задержка перед началом следующего преобразования после завершения предыдущего при последовательном переборе каналов (количество тактов).

28 тактов частоты C_ADC требуется на выполнение самого преобразования. Количество тактов DelayGO+1 частоты PCLKd используется для задержки перед преобразованием в циклическом режиме для заряда внутренней емкости АЦП.

Согласно спецификации на микроконтроллер в качестве источника синхросигнала АЦП f_C_ADC может быть выбрана либо частота PCLKd, либо ADC_CLK (см. рисунок 1). Настройка частоты ADC_CLK производится в блоке управления тактовыми частотами RST_CLK. Частота CPU_CLK для тактирования контроллера АЦП может быть настроена с помощью отдельного делителя частоты для АЦП. Коэффициент деления задаётся битами Cfg REG DIVCLK [3:0], регистр ADCx_CFG.

Дополнительная задержка перед началом преобразования всегда определяется в тактах частоты PCLKd, которая также поступает через делитель Cfg REG DIVCLK [3:0] и равна PCLK / (2^(Cfg REG DIVCLK).

Таким образом, при выборе источника синхросигнала C_ADC = PCLKd, установке DelayGO = 7, частоте тактирования микроконтроллера 80 МГц и делителе DIVCLK = 6, общее время преобразования будет равняться:

28*T_C_ADC + (DelayGO+1)*T_PCLKd = 28*T_PCLKd + 8*T_PCLKd = 36*T_PCLKd

f_PCLKd = PCLK / (2^Cfg REG DIVCLK) = 80 МГц / 64 = 1.25 МГц,

период T_PCLKd = 1/1.25 = 0.8 мкс,

общее время преобразования = 36*0.8 мкс = 28.8 мкс.

Однако, в МК К1986ВЕ92QI необходимо учитывать ошибку 0016 errata "Некорректное вычисление дополнительной задержки начала преобразования контроллера АЦП вариант 2", из-за которой дополнительная задержка, задаваемая битами DelayGO, вычисляется некорректно. На практике, к сожалению, расчёт дополнительной задержки зависит от многих факторов, и поэтому рассчитать теоретически данную задержку не получится, её можно измерить только экспериментально.

Сохранить статью в PDF